2026年3月开班计划:

FPGA逻辑开发班、FPGA测试定向班

开班时间:3月30日(预科)

开班地点:成都基地(成都ai创新中心)

夏令营开班计划:

开班时间:7月6日(暂定)

开班地点:成都基地(成都ai创新中心)

FPGA要学到什么程度才能进大厂?

那学习FPGA到什么程度才能够进入大厂工作呢?这应该是众多FPGA人才想要了解的问题。

近年来芯片正在国产化加速发展,经数据显示,中国FPGA市场的应用率不到30%,中国厂商FPGA产品在中国市场的份额总计不足5%,只有紫光同创、安路等厂商在中低密度市场取得了一些成绩,存在巨大的发展空间。在国家大力支持集成电路产业发展的环境下,对于尚不够强大的中国FPGA企业来说不失为黄金发展时机,因此众多企业在发展之际向众多FPGA人才抛出橄榄枝。

那学习FPGA到什么程度才能够进入大厂工作呢?

这应该是众多FPGA人才想要了解的问题。

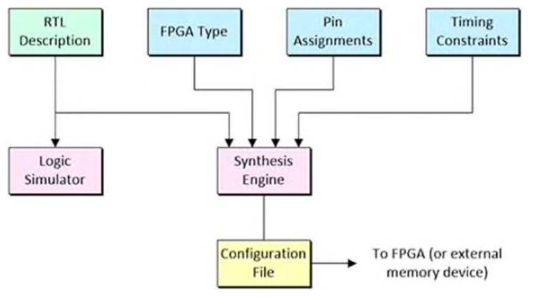

在入门FPGA时首先需要学习RTL编程语言、FPGA开发工具、数电以及实践方法,而从职业发展角度来看,FPGA人才们需要掌握RTL设计、验证技巧、FPGA的优化与约束等技能。

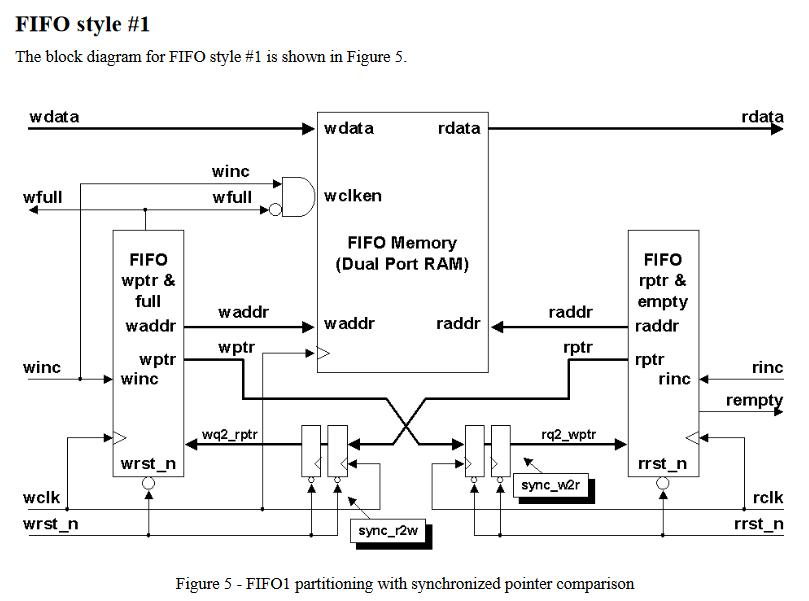

1、RTL设计的高级开发技巧RTL描述是可以表示为一个有限状态机或是一个可以在一个预定的时钟周期边界上进行寄存器传输的更一般的时序状态机。RTL设计中的跨时钟域处理的问题是企业在面试FPGA人才时经常会提到的问题,比如你会如何去处理一些多位不相关的信号、总线信号、脉冲等,这类问题主要是FIFO的设计,以及与其相关的一系列问题。

2、验证技巧验证的过程十分复杂,不仅需要进行实物的测试来确认功能是否实现,而是应该将测试验证嵌入到完整的设计流程中,从不同层次采用多种方法对软件功能、接口和性能进行确认,以保证FPGA测试验证的一致性,消除设计缺陷及隐患。在一个芯片中,平均每个芯片至少会花1/2的时间在验证上,有的甚至更多,而验证之所以会耗费开发人员如此多的精力和时间,是因为FPGA开发人员必须将所有的功能检查验证一遍。目前很多企业的工程师都会有专门的验证工程师和设计工程师,但验证和设计是每一个FPGA工程师应该掌握的技能。

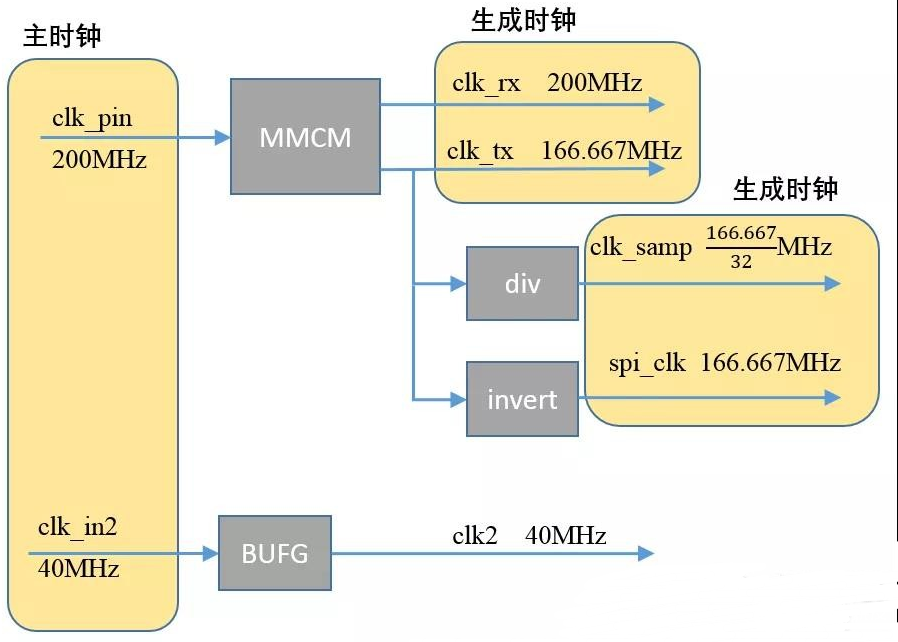

3、FPGA的约束和优化设计FPGA的优化设计最直接的作用就是提高模块的工作效率,FPGA约束的目的是为了设计而服务的,同时也是为了保证设计满足时序的要求,指导FPGA工具进行综合和实现,约束是Vivado等工具努力实现的目标。所以首先要设计合理,才可能满足约束,约束反过来检查设计能否满足时序。主要涉及到xilinx vivado xdc约束语法,给出对应的ISE ucf 语法。FPGA的约束和优化主要包括对时序、面积以及功耗等方面的约束,在FPGA设计和开发的过程中会始终穿插需要处理多个时钟情况如何处理、如何划定固定的设计区域以及设计的情况。而低功耗的FPGA设计由于时钟网络资源是固定,时钟树被关闭,所以门控时钟就不太适合。

4、职业相关技能除了掌握最主要的开发技术之外,FPGA工程师们还需要掌握一些硬实力,比如说很多公司的开发环境基本是Linux系统中进行,所以还需要掌握Linux的一些基本类似于Tcl、Perl、Makefile、Python等的口令;此外工程师们还需要具备基本的硬件调试能力,比如基本的FPGA板卡调试能力,对一个新的开发板从头开始调试。除此之外还包括一些软实力,比如语言沟通能力,这是很多FPGA工程师不重视的细节点,在和面试官进行面试时,良好的沟通也会是自己能力的一种展示,如果自己的实力不能很好地被表达出来,那再好的技术条件也会被埋没。

由于学习FPGA存在着一定的难度,要满足企业的要求也并非难事。成电少年学专注于集成电路和工业软件领域人才的培养,推出100天FPGA学习课程,线上线下同步学习,致力于培养我国自己的FPGA专业人才历经三年时间课程研发、沉淀,培养出来几千名合格的FPGA高级工程师,并成功进入到各个企业发挥价值。目前成电少年学已经为众多企业输送FPGA高级人才,薪资远超同届毕业生52%,就业率达100%。

- 适用人群:

- ① 计划从事FPGA工程师相关的在校大学生或教师;

- ② 计划实现高薪阶梯跨越的在职人员以及跨行业的在职人员;

- ③ 对FPGA想要深入学习的FPGA工程师;

- ④ 想尝试毕业后在集成电路行业发展的大一、大二、大三、大四在校生以及在校研究生;

- 希望通过成电少年学的FPGA课程学习,你能:

- ①掌握FPGA基础,培养出实践能力;

- ②深入了解FPGA开发流程和技巧;

- ③实现高薪跨越,月薪1W+;

福利大放送!!现在可以进行免费申请在线学习FPGA课程,抓紧时间,手慢则无!课程链接https://z.shaonianxue.cn。同学们可关注“成电少年学”公众号,FPGA行业最新资讯持续更新中~~

详情咨询:

陈老师:13219696129 (微信同步)

高老师:18935839030