以下是结合工程实践经验总结的7条FPGA学习核心方法论,涵盖思维模式、开发流程和避坑指南:

1. 硬件思维优先原则

典型误区:用软件思维写硬件代码

解决方案:

- 并行化设计:始终关注时钟周期内的逻辑级数

// 错误:顺序执行思维

always @(posedge clk) begin

a = b + c;

d = a * e; // 产生2级组合逻辑延迟

end

// 正确:流水线拆分

always @(posedge clk) begin

stage1 <= b + c;

end

always @(posedge clk) begin

stage2 <= stage1 * e;

end- 资源预评估:在编码前用Excel计算预估LUT/FF消耗量

- 时序敏感意识:关键路径标记(如

(* keep = "true" *))

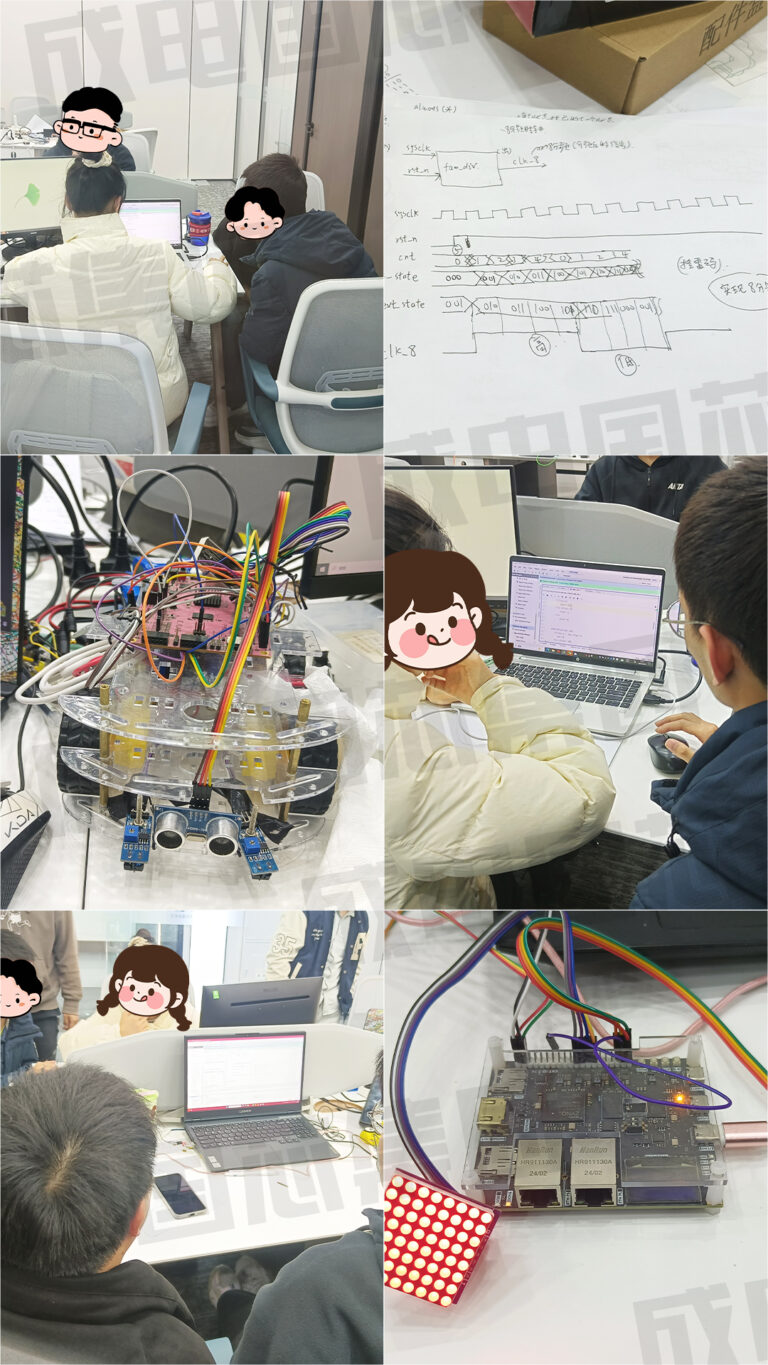

2. 仿真验证先行法则

血的教训:直接烧板调试导致定位困难

标准流程:

- 单元仿真:用ModelSim验证模块基础功能

- 系统仿真:Vivado XSIM验证跨模块交互

- 硬件验证:ChipScope抓取真实信号

验证技巧:

- 自动生成测试向量(Python脚本)

- 使用

$display实时输出仿真状态

3. 约束文件规范化

常见坑点:

- 时钟约束缺失导致时序违例

- 跨时钟域未添加

set_false_path

标准约束模板:

# 主时钟定义

create_clock -period 10 [get_ports clk]

# 生成时钟

create_generated_clock -divide_by 2 -source [get_ports clk] [get_pins clk_div/Q]

# 异步时钟域隔离

set_clock_groups -asynchronous -group {clk_100m} -group {clk_50m}推荐工具:Vivado Timing Constraints Wizard

4. 模块化设计习惯

代码管理规范:

功能解耦:单个模块不超过300行代码

参数化设计:

module fifo #(

parameter DATA_WIDTH = 32,

parameter DEPTH = 1024

)(

input wire clk,

output wire [DATA_WIDTH-1:0] dout

);3、版本控制:Git管理不同工程版本(.xpr文件需过滤)

5. 调试技巧体系化

三级调试法:

静态检查:

- Lint工具(SpyGlass)检查代码规范

- 综合后网表查看(

show_schematic)

动态分析:

- 关键信号打拍标记(

debug_前缀)

(* mark_debug = "true" *) reg [7:0] debug_counter;硬件实测:

- 分段隔离法:用PLL生成不同时钟域测试信号

6. 文档驱动开发

必要文档清单:

## 模块设计文档

### 功能规格

- 支持协议:IEEE 802.3

- 吞吐量:≥900Mbps

### 接口定义

| 信号名 | 方向 | 描述 |

|--------|------|--------------|

| clk | I | 125MHz主时钟 |

| data | O | 32位输出数据 |

### 测试用例

- Case1:连续发送1500字节帧

- Case2:错误帧过滤测试工具推荐:Doxygen自动生成文档

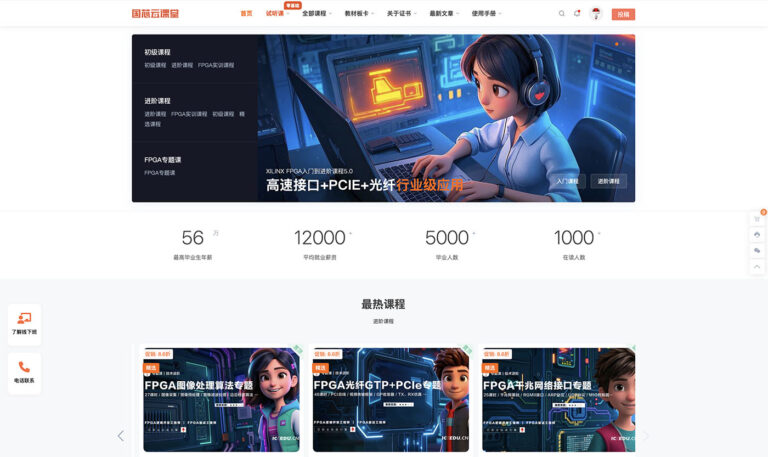

7. 持续知识更新

技术追踪清单:

- 协议更新:PCIe 6.0/CXL 2.0新特性

- 工具升级:Vivado 2023.1新增功能

- 国产替代:高云FPGA新型号特性解析

学习渠道:

- Xilinx/Altera官方Webinar

- GitHub热门项目(如VexRiscv)

- FPGA-Specific Subreddit技术讨论

实战避坑案例库

| 问题类型 | 典型表现 | 解决方案 |

|---|---|---|

| 时序收敛失败 | 建立时间违例 > 0.5ns | 插入寄存器 + 降频测试 |

| 亚稳态 | 随机性系统崩溃 | 双寄存器同步 + 格雷码编码 |

| 资源超限 | 布局布线失败 | 复用逻辑 + BRAM替换分布式RAM |

| 功耗超标 | 芯片发烫 > 85℃ | 时钟门控 + 动态频率调节 |

掌握这7大原则可减少70%的重复踩坑,如需具体案例的代码实现方案(如亚稳态处理或时序约束模板),可告知具体场景进一步展开! 🚀