工信部专业技能资格证+电研院专业技术证书

FPGA,现场可编程门阵列。以其低功耗、可重复编程的属性,被广泛运用到通讯,图像处理,高速信号处理以及人工智能计算加速等各个领域。日前教育部将集成电路设计规划为一级学科。而在集成电路设计中,FPGA也被广泛用于芯片的原型验证。

为加强国内FPGA领域的人才生态建设,加强全国高校教师在FPGA领域的深度交流,促进高等学校集成电路学科的教学改革,主动适应一级学科建设的需求,满足高校对人才培养的要求,提高人才培养质量和学生毕业就业率,加强课程体系与内容建设,成电少年学计划将于2022年11月至2023年1月举办“FPGA师资培训(寒假班)”。

此次FPGA师资培训将贯彻“打牢基础,学以致用、项目教学”的精神来开展。

具体有关事宜如下:

【面向对象】高校教师

【主办单位】工信部教育与考试中心、北方工业大学培训中心、成电少年学

【授课方式】线上直播授课

【培训费用】4800元/人。

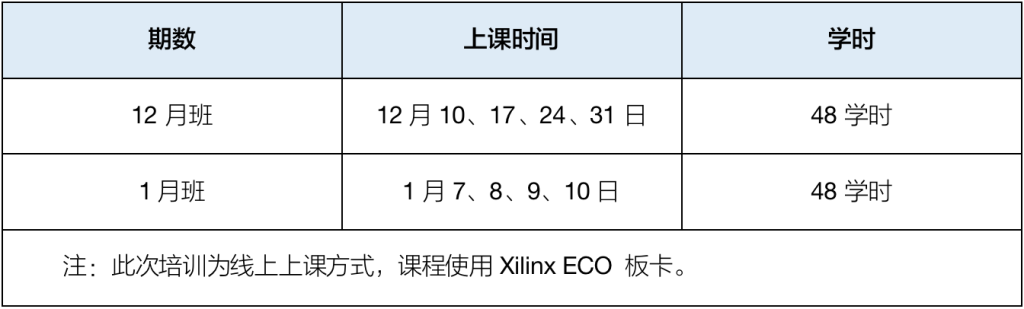

【培训时间】见下表

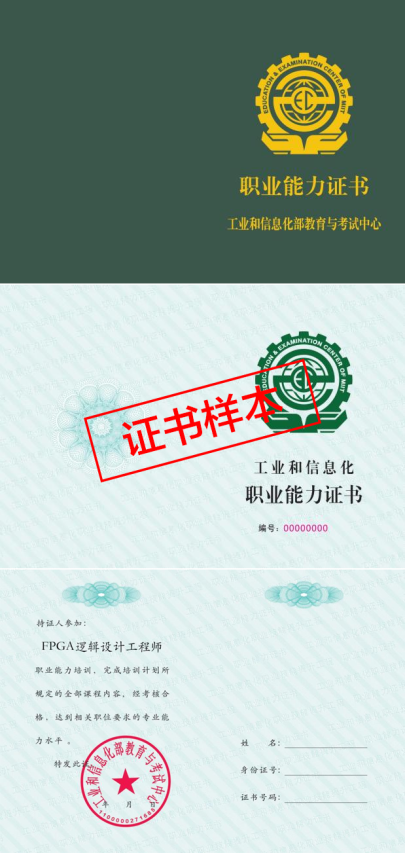

【结业证书】由工业和信息化部教育与考试中心颁发《工业和信息化职业能力证书》,学员信息纳入“工业和信息化技术技能人才库”,可在官网(www.miiteec.org.cn)查询。

一、培训目标

(一)零基础学习,工程案例,实训及课程方案;

(二)在编程环节,熟练掌握Verilog HDL编程语言、编程风格和编程技巧;

(三)实践掌握Vivado软件设计和诊断流程;

(四)分析学生作业,批改到硬件实现和讲解演示,领会教改环节贯穿项目驱动的要求;

(五)组织沙龙和结业活动,探讨数电课改的内容和方法,交流解决问题的经验和措施。

二、培训时间

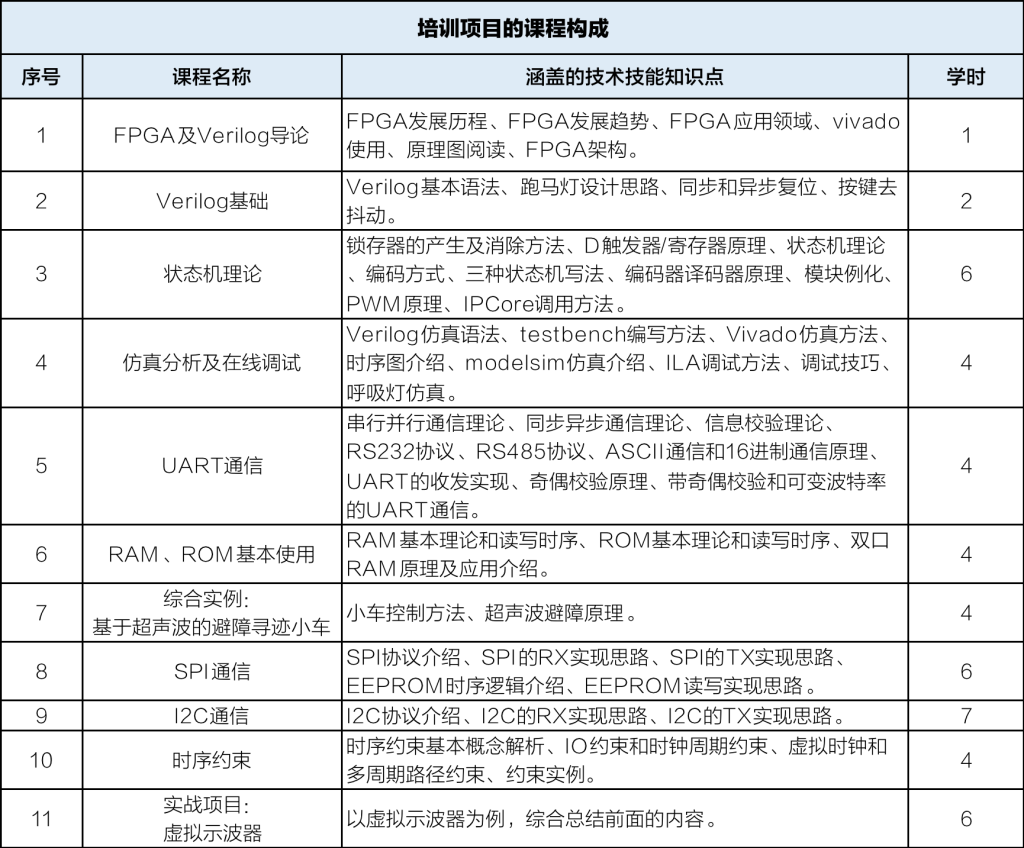

三、课程内容

四、证书

五、配套教材

教材介绍:

本教程为FPGA中级基础教程,内容包括FPGA仿真方法、时序分析、UART、SPI、IIC、RAM/ROM等基本使用方法和技巧。整本书分为三个部分,第一部分介绍FPGA仿真基本方法,第二部分介绍常用FPGA编程技巧,第三部分介绍时序约束方法。

第一部分介绍可用于FPGA仿真的Verilog语法、testbench编写方法、vivado仿真方法和modelsim仿真方法,通过该部分的学习,学生可以掌握基本的FPGA仿真流程和方法。

第二部分主要介绍FPGA编程中的基本方法和技巧。通过多个实验和仿真介绍了工业控制中经常用到的UART、SPI、IIC等通信方法;详细分析了FPGA编程中不可缺少的RAM/ROM、FIFO等的使用方法。通过该部分的学习,学生能够掌握FPGA编程中的基本通信方法和基本编程技巧。

第三部分介绍了FPGA编程中的难点——时序约束方法。首先,通过讲解FPGA静态时序分析理论,让学生了解时序分析和时序约束的原理;其次,通过介绍vivado的图形界面时序约束方法、TCL时序约束方法,进一步让学生了解FPGA时序约束的具体操作过程;最后,通过一个例子,讲解具体实例中时序约束的具体过程。

六、报名及费用

【报名方式】请学员将姓名、电话、身份证号码、邮寄地址和发票信息及一寸蓝底照片(以附件形式)发至报名邮箱snx@shaonianxue.cn。

【费用支付】

账户名称:成电少年学(广东)教育科技有限公司

账户号码:769910189210988

开户银行:招商银行股份有限公司东莞松山湖支行

【报名咨询电话】18996151919 张老师