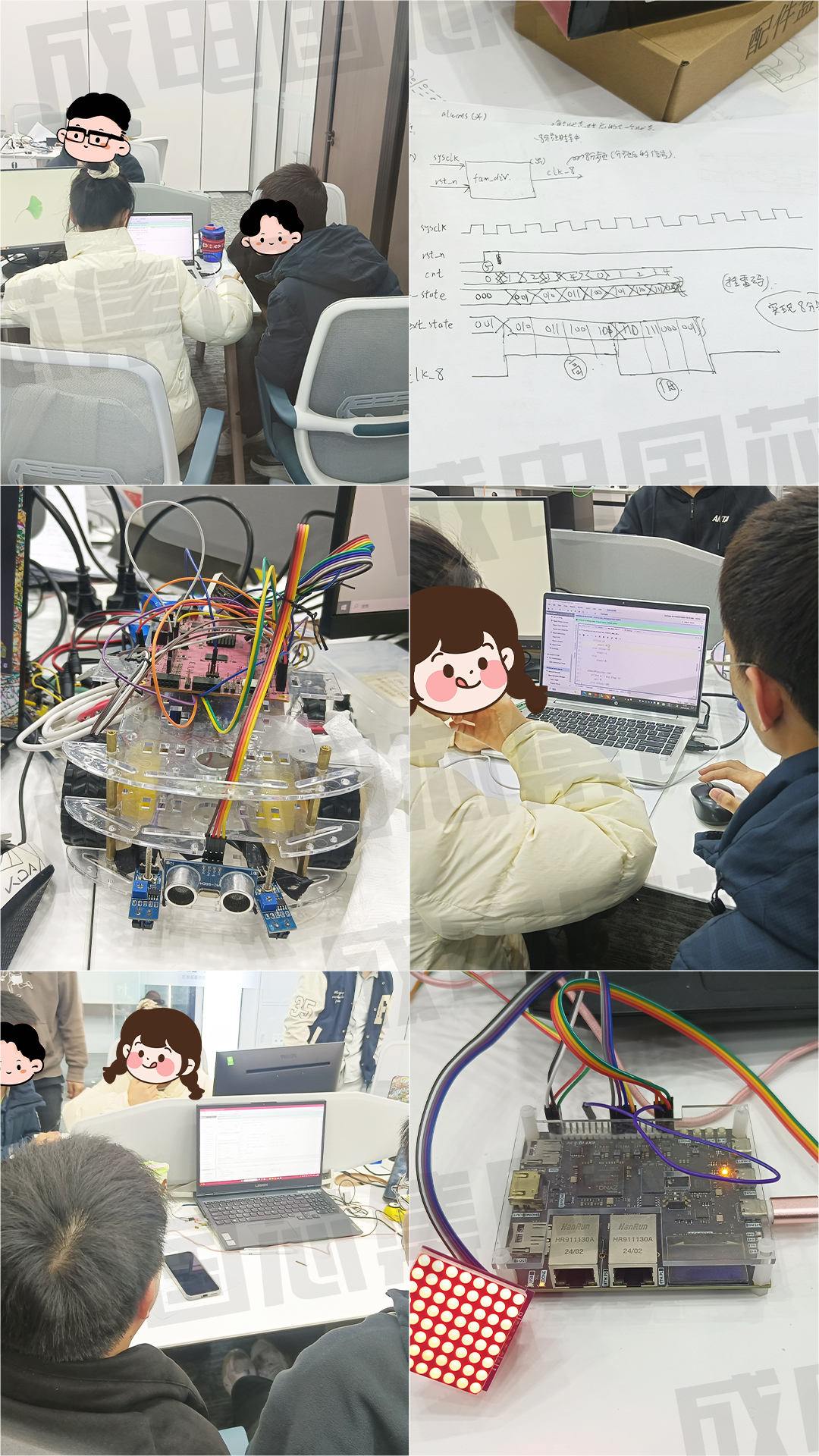

早上9点的成电国芯实训室内,键盘敲击声与示波器蜂鸣声已此起彼伏。当多数人还在享受周末懒觉时,FPGA就业班的学员们早已进入”工程模式”——有人正用Verilog在Xilinx Vivado里调试图像处理算法,有人在优化时序约束参数,更有小组激烈讨论着AXI总线协议在5G通信系统的应用方案。

【硬核实训场景直击】

在焊台区,三位学员正协作调试自制的PCIe数据采集卡。穿防静电服的张同学熟练使用逻辑分析仪抓取DDR3接口信号:”时序余量只剩0.3ns,必须重新计算CLK_SKEW”;操作万用表的李同学突然举手:”王工!这个BGA封装的电源引脚虚焊了”;而戴着护目镜的导师正指导如何用热风枪精准补焊。这种工业级实战环境,让学员提前适应企业级开发标准。

【项目驱动式学习】

教室内投影着某智慧交通项目的系统架构图,三十余名学员正分组攻坚FPGA加速方案。算法组在用Matlab建模车道识别CNN,硬件组在ISE里综合交通灯控制IP核,接口组则调试着千兆以太网传输协议。突然,调试摄像头的组员发现DMA传输丢帧,瞬间引发多组联合攻关:从时序约束调整到DDR控制器优化,最终在Spartan-6开发板上实现了120fps的稳定传输。

【企业级开发全流程】

走廊公告栏贴着各小组的Gantt图进度表:需求分析-架构设计-模块开发-系统集成-压力测试。每个环节都对应企业真实开发流程。正在编写UVM验证环境的刘同学说:”上周刚完成AXI VIP搭建,这周要配合算法组做覆盖率驱动验证。”这种从RTL设计到验证的全链条实践,让学员毕业即具备中级工程师能力。

【名师零距离指导】

实训台前,拥有15年FPGA开发经验的陈工正在演示JESD204B接口调试技巧:”注意Rx_SYNC信号要与帧时钟严格对齐,这个参数设置偏差1%就会导致链路失步。”学员们围着Xilinx Zynq Ultrascale+开发板,实时观察着ILA捕获的串行数据眼图。这种手把手的工程经验传授,正是培训班区别于院校教育的核心价值。

【成果可视化进阶】

教室后方的展示区陈列着学员作品:支持OpenCL的AI加速卡、符合TSN标准的工业交换机、医疗超声波束合成器…每件作品都对应着真实岗位需求。正在调试HDMI输入输出的赵同学分享:”完成这个视频处理系统后,突然理解了秋招时企业的FPGA岗位要求。”

成电国芯的周末课堂没有枯燥的理论灌输,有的只是此起彼伏的”bit文件生成成功”提示音、调试通过时的欢呼声、以及键盘上飞舞着追逐梦想的指尖。当其他人在刷短视频时,这群未来的FPGA工程师正在用代码编织硬件的灵魂,用示波器丈量技术的边界。他们的每个周末,都在为斩获25-40万年薪的offer积累决胜筹码。

【加入我们】

如果你也渴望:

√ 掌握Xilinx/Altera全系开发工具链

√ 参与5G/AI/自动驾驶等前沿项目实战

√ 获得华为/中兴/大疆等名企内推机会

成电国芯FPGA就业班,用30个周末的沉浸式实训,助你实现从电子爱好者到资深工程师的华丽蜕变!