赛灵思FPGA芯片内部架构可以分为5个层级,因为现在用的是XC7Z020芯片,因此可分别为BEL层、Site层、Tile层、FSR层及Device层。

SLICE_X38Y59/F7BMUX

在学习前可以先了解一下内部的逻辑器件名称SLICE_X38Y59/F7BMUX的意思

1. FPGA的结构基础

FPGA是由大量的可编程逻辑单元和其他资源组成的。这些逻辑单元被组织成一种二维的阵列结构,就像一个棋盘一样。

SLICE是这个“棋盘”中的一个小方格,它是FPGA内部实现逻辑功能的基本构建块之一。每个SLICE都有自己独特的位置标识,这就是X和Y坐标的作用。

2. 坐标的意义

X38Y61中的X和Y就像地图上的横坐标和纵坐标。X坐标表示在FPGA芯片的水平方向上的位置,Y坐标表示在垂直方向上的位置。

例如,如果把FPGA芯片想象成一个城市的地图,那么每个SLICE就像城市中的一个街区,而X38Y61就是这个街区在地图上的具体位置,这样工程师就可以准确地找到并使用这个特定的SLICE来构建他们需要的逻辑电路。

3. SLICE的内部资源

每个SLICE内部包含了一些关键的可编程逻辑资源。其中最常见的是查找表(LUT)和寄存器。

查找表可以实现各种逻辑函数。比如说,你可以把它想象成一个预先设置好规则的“黑盒子”,当输入某些信号时,它会根据内部设置的规则输出相应的结果。

寄存器则用于存储数据和状态信息。它就像一个小的“存储单元”,可以在时钟信号的控制下保存数据,并在需要的时候提供这些数据给其他电路部分。

F7AMUX

1. 多路复用器的概念

多路复用器(MUX)是一种在电子电路中非常常见的器件。它的基本作用是从多个输入信号中选择一个信号并输出。

可以把它想象成一个有多个入口和一个出口的“开关盒子”。根据控制信号的不同,它会选择不同的入口信号并从出口输出。

在FPGA中它主要用于在SLICE内部的不同逻辑资源之间进行信号的选择和路由。

BEL

这一层,可以理解为FPGA内部的基本逻辑单元,是最底层的单元,后面所有的层级可以理解为就是这一层进行叠加的。

Bel一般分为两类,分别为布线类bel和逻辑类bel。

下面打开Device界面来进行观看,

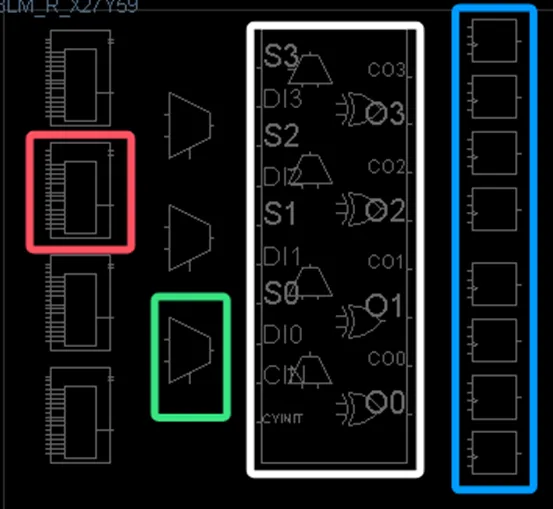

这个就是整个的界面,接下来只需要一直放大就行,放大到这个界面后就可以看到逻辑BEL了。

这里面有四种逻辑bel,蓝色框的是FF(触发器),红色框的是LUT(查找表),绿色框是复用器,白色框可以理解为简单的DSP资源。

对于bel这一层而言,除了逻辑资源外还有布线资源,如图:

它的作用就是用来连接各个逻辑点。

Site层

对于这一层也有两种,一种可以理解为是上述两图中的bel层的集成版,如图:

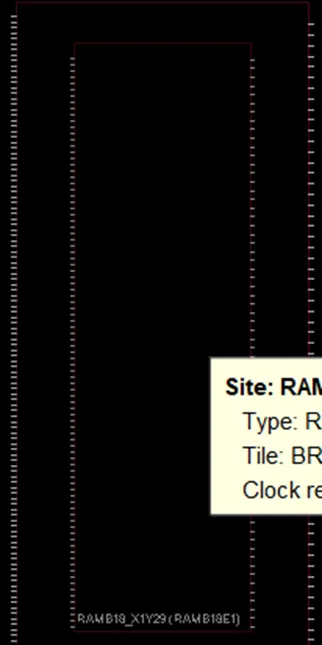

另一种是内部的ram、PLL这些固核组成的,如图:

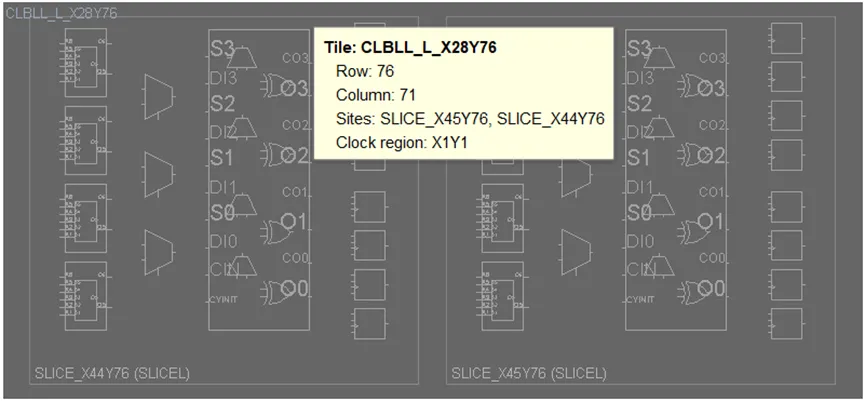

Tile

对于这一层可以理解为就是两个site的组合,又称为CLB(可编程逻辑块)。

它的作用就是组成一个四输入,CLB越多也代表内部资源更多,调用CLB可以使内部的控制更加简洁,至于为什么是两个组成(跟架构有关系-设计的点更多这里就不赘述了)。

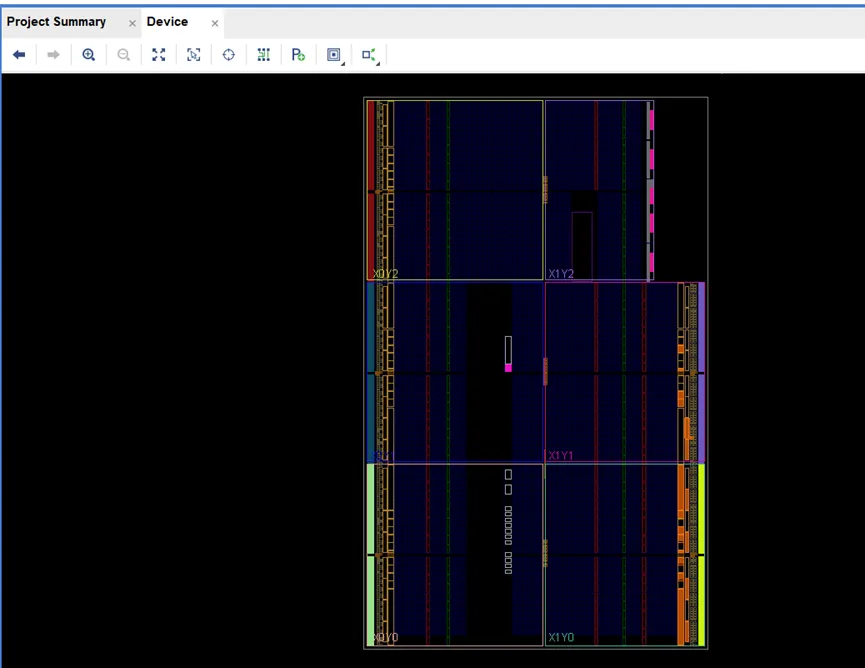

FSR

可以把他理解为时钟域、这里需要注意的是,咱们在原理图或者Package界面中看到的是bank区域并不是时钟区域,时钟域!=bank。时钟域如图:

最后就是Device了,这个可以理解为一个芯片的资源。

Device

上述为FPGA内部架构,那么FPGA由哪些组成呢,FPGA一般由CLB(可配置逻辑资源),IOB(输入/输出块),可编程互联线,block RAM,时钟管理单元(PLL,MMCM),DSP和IP核等。

1、 CLB

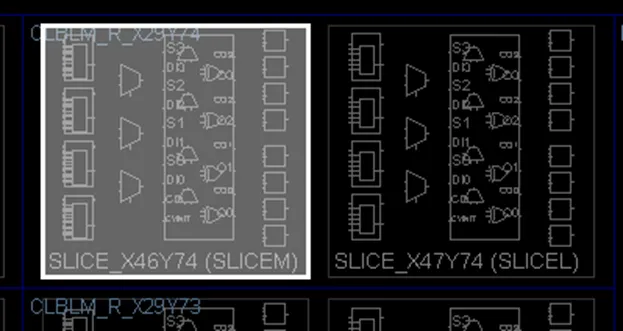

CLB是实现逻辑功能的基本单元,一个CLB由2个slice组成,slice可以分成以下的两类:SliceM(Memory)和SliceL(Logic)。这两种slice的区别在于它们的LUT不同。

SLICEM(M:Memory):其内部的LUT可以读也可以写,可以实现移位寄存器和64bit的DRAM等存储功能,还可以实现基本的查找表逻辑。

SLICEL(L:Logic):其内部的LUT只可以读,只能实现基本的查找表逻辑。

2、IOB(可编程输入输出单元,Input/Output Block)

FPGA的IOB是输入/输出块(Input/Output Block)的简称,它是FPGA内部实现复杂逻辑的关键部分,负责处理输入输出信号。IOB内部包含了一系列的逻辑单元,用以完成信号的缓冲、驱动、映射等功能。

在Xilinx的FPGA中,IOB内部结构可以简化为以下几个主要部分:

输入缓冲器(Input Buffers):用于提高信号的鲁棒性和减少信号的噪声干扰。

输出驱动器(Output Drivers):负责将FPGA内部逻辑单元的信号驱动到IOB外部。

并串转换(Serial-to-Parallel and Parallel-to-Serial Converters):用于实现信号的串并转换,以适应不同位宽的信号传输。

控制逻辑(Control Logic):负责处理IOB的各种配置和功能控制信号。

3、时钟管理单元

区域(Region):每个FPGA器件被分为多个区域,不同的型号的器件区域数量不同。FPGA时钟资源主要有三大类:时钟管理单元、时钟IO、时钟布线资源。

时钟管理模块:不同厂家及型号的FPGA中的时钟管理资源会有一些差异,主要功能是对时钟的频率、占空比、相位等功能的管理。例如:PLL,DLL,DCM,MMCM(混合模式时钟管理器)等。

时钟IO,FPGA的时钟IO分布在不同的区域。像xilinx的时钟IO分为MRCC(全局时钟pin)和SRCC(局部时钟pin)。

Clock Routing Source:时钟布线资源含有时钟线以及时钟缓冲器,数量上会比前两者多;含全局时钟网络(GCLK)和局部时钟网络(RCLK)的时钟线及缓冲(BUFG,BUFR等)。

详情咨询:李老师:18008385791